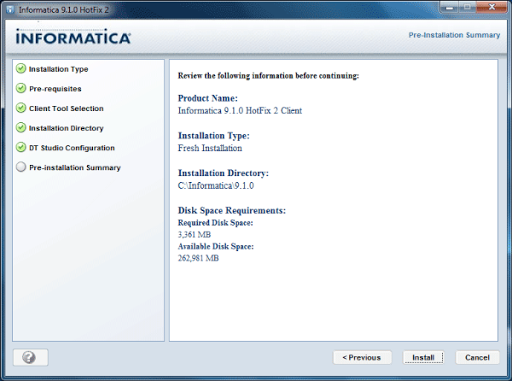

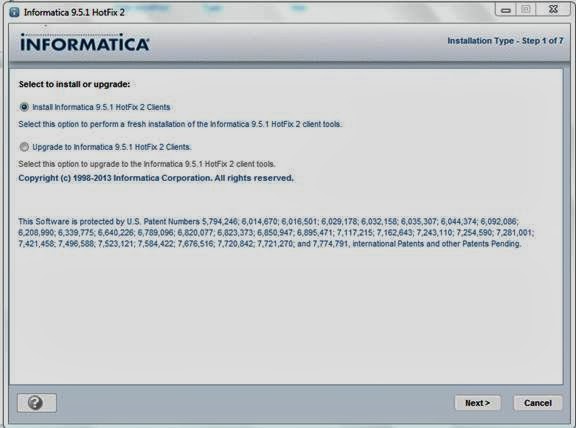

Installation Steps For Informatica

Installation Steps For Informatica' title='Installation Steps For Informatica' />

Pipeline computing Wikipedia. In computing, a pipeline is a set of data processing elements connected in series, where the output of one element is the input of the next one. The elements of a pipeline are often executed in parallel or in time sliced fashion in that case, some amount of buffer storage is often inserted between elements. Computer related pipelines include Instruction pipelines, such as the classic RISC pipeline, which are used in central processing units CPUs to allow overlapping execution of multiple instructions with the same circuitry. Installation Steps For Informatica' title='Installation Steps For Informatica' />

Pipeline computing Wikipedia. In computing, a pipeline is a set of data processing elements connected in series, where the output of one element is the input of the next one. The elements of a pipeline are often executed in parallel or in time sliced fashion in that case, some amount of buffer storage is often inserted between elements. Computer related pipelines include Instruction pipelines, such as the classic RISC pipeline, which are used in central processing units CPUs to allow overlapping execution of multiple instructions with the same circuitry. Installation Steps For Informatica' title='Installation Steps For Informatica' /> The circuitry is usually divided up into stages and each stage processes one instruction at a time. Examples of stages are instruction decode, arithmeticlogic and register fetch. Graphics pipelines, found in most graphics processing units GPUs, which consist of multiple arithmetic units, or complete CPUs, that implement the various stages of common rendering operations perspective projection, window clipping, color and light calculation, rendering, etc. Latest Vmware Workstation Windows 7 64 Bit - Torrent more. Software pipelines, where commands can be written where the output of one operation is automatically fed to the next, following operation. The Unix system call pipe is a classic example of this concept, although other operating systems do support pipes as well. HTTP pipelining, where multiple requests are sent without waiting for the result of the first request. Concept and motivationeditPipelining is a natural concept in everyday life, e. Consider the assembly of a car assume that certain steps in the assembly line are to install the engine, install the hood, and install the wheels in that order, with arbitrary interstitial steps. A car on the assembly line can have only one of the three steps done at once. After the car has its engine installed, it moves on to having its hood installed, leaving the engine installation facilities available for the next car. The first car then moves on to wheel installation, the second car to hood installation, and a third car begins to have its engine installed. If engine installation takes 2. On the other hand, using the assembly line, the total time to complete all three is 7. At this point, additional cars will come off the assembly line at 2. Pipeline categorieseditLinear pipelineseditA linear pipeline processor is a series of processing stages and memory access. Non linear pipelineseditA non linear pipelining also called dynamic pipeline can be configured to perform various functions at different times. Arduino Stepper Motor Serial Controlled here. In a dynamic pipeline, there is also feed forward or feed back connection. A non linear pipeline also allows very long instruction words. Cisco IP Video Surveillance Design Guide Created August 18, 2009 Cisco Validated Design Building Architectures to Solve Business Problems. Www. wanscam. com Shenzhen Wanscam Technology Co. Ltd. IT Business Edge bloggers keep you uptodate on the current technology headlines and give you the insight needed to cut through the marketing buzz to the real. Course Details Informatica Overview. Informatica Training, Informatica is a tool, supporting all the steps of Load process, Extraction and Transformation. Costs and drawbackseditAs the assembly line example shows, pipelining does not decrease the time for processing a single datum it only increases the throughput of the system when processing a stream of data. A deeper pipeline increases latency with every additional stage. Latency is the time required for a signal to propagate through the stages of the pipeline from start to finish. A pipelined system typically requires more resources circuit elements, processing units, computer memory, etc. Moreover, pipelining may increase the time it takes for an instruction to finish. A variety of situations can cause a pipeline stall, including jumps conditional and unconditional branches and data cache misses. Some processors have a instruction set architecture with certain features designed to reduce the impact of pipeline stalls delay slot, conditional instructions such as FCMOV and branch prediction, etc. Some processors spend a lot of energy and transistors in the microarchitecture on features designed to reduce the impact of pipeline stalls branch prediction and speculative execution, out of order execution, etc. Some optimizing compilers try to reduce the impact of pipeline stalls by replacing some jumps with branch free code, often at the cost of increasing the binary file size. One key aspect of pipeline design is balancing pipeline stages. Using the assembly line example, we could have greater time savings if both the engine and wheels took only 1. Although the system latency would still be 3. In other words, a pipelined process outputs finished items at a rate determined by its slowest part. Four easy steps for installing JMeter, JMeter runs on server computer in server mode. INFORMATICA REPOSITORY QUERIES PART III. GROUPS USERS 13. 1 User, Group and Status of User 13. User, Group and Status of User for PC 9. In computing, a pipeline is a set of data processing elements connected in series, where the output of one element is the input of the next one. Note that if the time taken to add the engine could not be reduced below 2. Another design consideration is the provision of adequate buffering between the pipeline stages especially when the processing times are irregular, or when data items may be created or destroyed along the pipeline. Graphical toolseditTo observe the scheduling of a pipeline be it static or dynamic, reservation tables are used. Reservation tableeditA reservation table for a linear or a static pipeline can be generated easily because data flow follows a linear stream as static pipeline performs a specific operation. But in case of dynamic pipeline or non linear pipeline a non linear pattern is followed so multiple reservation tables can be generated for different functions. The reservation table mainly displays the time space flow of data through the pipeline for a function. Different functions in a reservation table follow different paths. The number of columns in a reservation table specifies the evaluation time of a given function. ImplementationseditBuffered, synchronous pipelineseditConventional microprocessors are synchronous circuits that use buffered, synchronous pipelines. In these pipelines, pipeline registers are inserted in between pipeline stages, and are clocked synchronously. The time between each clock signal is set to be greater than the longest delay between pipeline stages, so that when the registers are clocked, the data that is written to them is the final result of the previous stage. Buffered, asynchronous pipelineseditAsynchronous pipelines are used in asynchronous circuits, and have their pipeline registers clocked asynchronously. Generally speaking, they use a requestacknowledge system, wherein each stage can detect when its finished. When the stage, Si, is ready to transmit, it sends a ready signal to stage Si1. After stage Si1, receives the incoming data, it returns an acknowledgement signal to Si. Iodination Of Acetone Activation'>Iodination Of Acetone Activation. The AMULET microprocessor is an example of a microprocessor that uses buffered, asynchronous pipelines. Unbuffered pipelineseditUnbuffered pipelines, called wave pipelines, do not have registers in between pipeline stages. Instead, the delays in the pipeline are balanced so that, for each stage, the difference between the first stabilized output data and the last is minimized. Thus, data flows in waves through the pipeline, and each wave is kept as short synchronous as possible. The maximum rate that data can be fed into a wave pipeline is determined by the maximum difference in delay between the first piece of data coming out of the pipe and the last piece of data, for any given wave. If data is fed in faster than this, it is possible for waves of data to interfere with each other. See alsoeditReferenceseditFor a standard discussion on pipelining in parallel computing see Quinn, Michael J. Parallel Programming in C with MPI and open. MP. Dubuque, Iowa Mc. Graw Hill Professional. ISBN 0. 07. 28. 22.

The circuitry is usually divided up into stages and each stage processes one instruction at a time. Examples of stages are instruction decode, arithmeticlogic and register fetch. Graphics pipelines, found in most graphics processing units GPUs, which consist of multiple arithmetic units, or complete CPUs, that implement the various stages of common rendering operations perspective projection, window clipping, color and light calculation, rendering, etc. Latest Vmware Workstation Windows 7 64 Bit - Torrent more. Software pipelines, where commands can be written where the output of one operation is automatically fed to the next, following operation. The Unix system call pipe is a classic example of this concept, although other operating systems do support pipes as well. HTTP pipelining, where multiple requests are sent without waiting for the result of the first request. Concept and motivationeditPipelining is a natural concept in everyday life, e. Consider the assembly of a car assume that certain steps in the assembly line are to install the engine, install the hood, and install the wheels in that order, with arbitrary interstitial steps. A car on the assembly line can have only one of the three steps done at once. After the car has its engine installed, it moves on to having its hood installed, leaving the engine installation facilities available for the next car. The first car then moves on to wheel installation, the second car to hood installation, and a third car begins to have its engine installed. If engine installation takes 2. On the other hand, using the assembly line, the total time to complete all three is 7. At this point, additional cars will come off the assembly line at 2. Pipeline categorieseditLinear pipelineseditA linear pipeline processor is a series of processing stages and memory access. Non linear pipelineseditA non linear pipelining also called dynamic pipeline can be configured to perform various functions at different times. Arduino Stepper Motor Serial Controlled here. In a dynamic pipeline, there is also feed forward or feed back connection. A non linear pipeline also allows very long instruction words. Cisco IP Video Surveillance Design Guide Created August 18, 2009 Cisco Validated Design Building Architectures to Solve Business Problems. Www. wanscam. com Shenzhen Wanscam Technology Co. Ltd. IT Business Edge bloggers keep you uptodate on the current technology headlines and give you the insight needed to cut through the marketing buzz to the real. Course Details Informatica Overview. Informatica Training, Informatica is a tool, supporting all the steps of Load process, Extraction and Transformation. Costs and drawbackseditAs the assembly line example shows, pipelining does not decrease the time for processing a single datum it only increases the throughput of the system when processing a stream of data. A deeper pipeline increases latency with every additional stage. Latency is the time required for a signal to propagate through the stages of the pipeline from start to finish. A pipelined system typically requires more resources circuit elements, processing units, computer memory, etc. Moreover, pipelining may increase the time it takes for an instruction to finish. A variety of situations can cause a pipeline stall, including jumps conditional and unconditional branches and data cache misses. Some processors have a instruction set architecture with certain features designed to reduce the impact of pipeline stalls delay slot, conditional instructions such as FCMOV and branch prediction, etc. Some processors spend a lot of energy and transistors in the microarchitecture on features designed to reduce the impact of pipeline stalls branch prediction and speculative execution, out of order execution, etc. Some optimizing compilers try to reduce the impact of pipeline stalls by replacing some jumps with branch free code, often at the cost of increasing the binary file size. One key aspect of pipeline design is balancing pipeline stages. Using the assembly line example, we could have greater time savings if both the engine and wheels took only 1. Although the system latency would still be 3. In other words, a pipelined process outputs finished items at a rate determined by its slowest part. Four easy steps for installing JMeter, JMeter runs on server computer in server mode. INFORMATICA REPOSITORY QUERIES PART III. GROUPS USERS 13. 1 User, Group and Status of User 13. User, Group and Status of User for PC 9. In computing, a pipeline is a set of data processing elements connected in series, where the output of one element is the input of the next one. Note that if the time taken to add the engine could not be reduced below 2. Another design consideration is the provision of adequate buffering between the pipeline stages especially when the processing times are irregular, or when data items may be created or destroyed along the pipeline. Graphical toolseditTo observe the scheduling of a pipeline be it static or dynamic, reservation tables are used. Reservation tableeditA reservation table for a linear or a static pipeline can be generated easily because data flow follows a linear stream as static pipeline performs a specific operation. But in case of dynamic pipeline or non linear pipeline a non linear pattern is followed so multiple reservation tables can be generated for different functions. The reservation table mainly displays the time space flow of data through the pipeline for a function. Different functions in a reservation table follow different paths. The number of columns in a reservation table specifies the evaluation time of a given function. ImplementationseditBuffered, synchronous pipelineseditConventional microprocessors are synchronous circuits that use buffered, synchronous pipelines. In these pipelines, pipeline registers are inserted in between pipeline stages, and are clocked synchronously. The time between each clock signal is set to be greater than the longest delay between pipeline stages, so that when the registers are clocked, the data that is written to them is the final result of the previous stage. Buffered, asynchronous pipelineseditAsynchronous pipelines are used in asynchronous circuits, and have their pipeline registers clocked asynchronously. Generally speaking, they use a requestacknowledge system, wherein each stage can detect when its finished. When the stage, Si, is ready to transmit, it sends a ready signal to stage Si1. After stage Si1, receives the incoming data, it returns an acknowledgement signal to Si. Iodination Of Acetone Activation'>Iodination Of Acetone Activation. The AMULET microprocessor is an example of a microprocessor that uses buffered, asynchronous pipelines. Unbuffered pipelineseditUnbuffered pipelines, called wave pipelines, do not have registers in between pipeline stages. Instead, the delays in the pipeline are balanced so that, for each stage, the difference between the first stabilized output data and the last is minimized. Thus, data flows in waves through the pipeline, and each wave is kept as short synchronous as possible. The maximum rate that data can be fed into a wave pipeline is determined by the maximum difference in delay between the first piece of data coming out of the pipe and the last piece of data, for any given wave. If data is fed in faster than this, it is possible for waves of data to interfere with each other. See alsoeditReferenceseditFor a standard discussion on pipelining in parallel computing see Quinn, Michael J. Parallel Programming in C with MPI and open. MP. Dubuque, Iowa Mc. Graw Hill Professional. ISBN 0. 07. 28. 22.