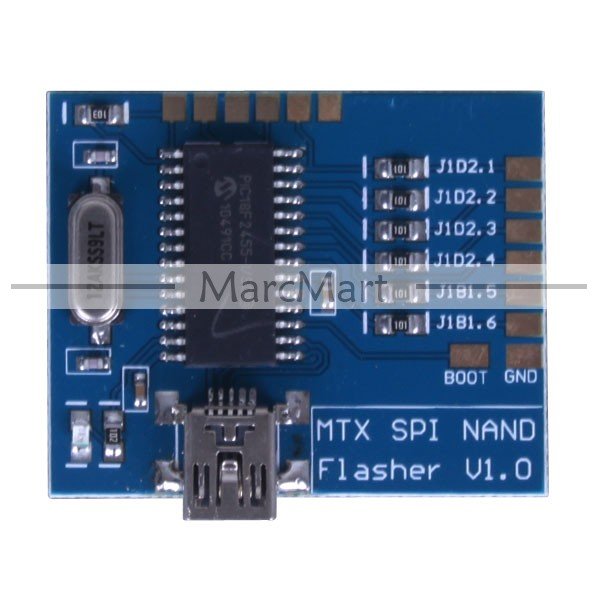

Driver Matrix Spi Nand Flasher

STM3. 2L4. 76. VG Ultra low power with FPU ARM Cortex M4 MCU 8. MHz with 1 Mbyte Flash, LCD, USB OTG, DFSDMThe STM3. L4. 76xx devices are the ultra low power microcontrollers based on the high performance ARM Cortex M4 3. RISC core operating at a frequency of up to 8. MHz. The Cortex M4 core features a Floating point unit FPU single precision which supports all ARM single precision data processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit MPU which enhances application security. The STM3. 2L4. 76xx devices embed high speed memories Flash memory up to 1 Mbyte, up to 1. Kbyte of SRAM, a flexible external memory controller FSMC for static memories for devices with packages of 1. Introduction. Please note that most of these Brand Names are registered Trade Marks, Company Names or otherwise controlled and their inclusion in this index is. B. Bitte newsde. newusers. Realnamensdiskussion nicht stndig mit falschen Behauptungen neu aufrollen. CIRCUITOS INTEGRADOS Puede utilizar los filtros a continuacin para encontrar rpidamente el integrado que necesita. Issuu is a digital publishing platform that makes it simple to publish magazines, catalogs, newspapers, books, and more online. Easily share your publications and get. Quad SPI flash memories interface available on all packages and an extensive range of enhanced IOs and peripherals connected to two APB buses, two AHB buses and a 3. AHB bus matrix. The STM3. L4. 76xx devices embed several protection mechanisms for embedded Flash memory and SRAM readout protection, write protection, proprietary code readout protection and Firewall. The devices offer up to three fast 1. ADCs 5 Msps, two comparators, two operational amplifiers, two DAC channels, an internal voltage reference buffer, a low power RTC, two general purpose 3. PWM timers dedicated to motor control, seven general purpose 1. The devices support four digital filters for external sigma delta modulators DFSDM. Autodesk 3Ds Max 2013 32 Bit Serial Number there. Copy.jpg' alt='Driver Matrix Spi Nand Flasher' title='Driver Matrix Spi Nand Flasher' />International Journal of Engineering Research and Applications IJERA is an open access online peer reviewed international journal that publishes research. Driver Matrix Spi Nand Flasher' title='Driver Matrix Spi Nand Flasher' /> In addition, up to 2. The devices also embed an integrated LCD driver 8x. They also feature standard and advanced communication interfaces. The STM3. 2L4. 76xx operates in the 4. C 1. 05 C junction, 4. C 1. 25 C junction and 4. C 1. 30 C junction temperature ranges from a 1. V VDD power supply when using internal LDO regulator and a 1. V VDD1. 2 power supply when using external SMPS supply. A comprehensive set of power saving modes allows the design of low power applications. Some independent power supplies are supported analog independent supply input for ADC, DAC, OPAMPs and comparators, 3. V dedicated supply input for USB and up to 1. IOs can be supplied independently down to 1. V. A VBAT input allows to backup the RTC and backup registers. Dedicated VDD1. 2 power supplies can be used to bypass the internal LDO regulator when connected to an external SMPS. The STM3. 2L4. 76xx family offers six packages from 6. Key Features. Ultra low power with Flex. Power. Control. 1. V to 3. 6 V power supply 4. C to 8. 51. 051.

In addition, up to 2. The devices also embed an integrated LCD driver 8x. They also feature standard and advanced communication interfaces. The STM3. 2L4. 76xx operates in the 4. C 1. 05 C junction, 4. C 1. 25 C junction and 4. C 1. 30 C junction temperature ranges from a 1. V VDD power supply when using internal LDO regulator and a 1. V VDD1. 2 power supply when using external SMPS supply. A comprehensive set of power saving modes allows the design of low power applications. Some independent power supplies are supported analog independent supply input for ADC, DAC, OPAMPs and comparators, 3. V dedicated supply input for USB and up to 1. IOs can be supplied independently down to 1. V. A VBAT input allows to backup the RTC and backup registers. Dedicated VDD1. 2 power supplies can be used to bypass the internal LDO regulator when connected to an external SMPS. The STM3. 2L4. 76xx family offers six packages from 6. Key Features. Ultra low power with Flex. Power. Control. 1. V to 3. 6 V power supply 4. C to 8. 51. 051.

C temperature range. A in VBAT mode supply for RTC and 3. A Shutdown mode 5 wakeup pins1. A Standby mode 5 wakeup pins4. A Standby mode with RTC1. A Stop 2 mode, 1. A with RTC1. 00 AMHz run mode LDO Mode3. AMHz run mode 3. V SMPS ModeBatch acquisition mode BAM4 s wakeup from Stop mode. Brown out reset BORInterconnect matrix. Core ARM 3. 2 bit Cortex M4 CPU with FPU, Adaptive real time accelerator ART Accelerator allowing 0 wait state execution from Flash memory, frequency up to 8. MHz, MPU, 1. 00. DMIPS and DSP instructions. Performance benchmark. DMIPSMHz Drystone 2. Core. Mark 3. 4. Core. MarkMHz 8. MHzEnergy benchmark. Clock Sources. 4 to 4. MHz crystal oscillator. Hz crystal oscillator for RTC LSEInternal 1. MHz factory trimmed RC 1Internal low power 3. Hz RC 5Internal multispeed 1. Hz to 4. 8 MHz oscillator, auto trimmed by LSE better than 0. PLLs for system clock, USB, audio, ADCUp to 1. IOs, most 5 V tolerant, up to 1. IOs with independent supply down to 1. V. RTC with HW calendar, alarms and calibration. LCD 8 4. 0 or 4 4. Up to 2. 4 capacitive sensing channels support touchkey, linear and rotary touch sensors. Stop mode, 2x watchdogs, Sys. Tick timer. Up to 1 MB Flash, 2 banks read while write, proprietary code readout protection. Up to 1. 28 KB of SRAM including 3. KB with hardware parity check. External memory interface for static memories supporting SRAM, PSRAM, NOR and NAND memories. Quad SPI memory interface. Rich analog peripherals independent supply. ADC 5 Msps, up to 1. AMsps. 2x 1. 2 bit DAC, low power sample and hold. PGA2x ultra low power comparators. USB OTG 2. 0 full speed, LPM and BCD2x SAIs serial audio interface3x I2. C FM1 Mbits, SMBusPMBus. USARTs ISO 7. 81. LIN, Ir. DA, modem1x LPUART Stop 2 wake up3x SPIs 4x SPIs with the Quad SPICAN 2. B Active and SDMMC interface. SWPMI single wire protocol master IFIRTIM Infrared interface1. DMA controller. True random number generator. CRC calculation unit, 9. ID. Development support serial wire debug SWD, JTAG, Embedded Trace Macrocell. STM3. 2F7. 67. NI High performance and DSP with FPU, ARM Cortex M7 MCU with 2 Mbytes Flash, 2. MHz CPU, Art Accelerator, L1 cache, SDRAM, TFT, JPEG codec, DFSDMThe STM3. F7. 65xx, STM3. 2F7. STM3. 2F7. 68. Ax and STM3. F7. 69xx devices are based on the high performance Arm Cortex M7 3. RISC core operating at up to 2. MHz frequency. The Cortex M7 core features a floating point unit FPU which supports Arm double precision and single precision data processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit MPU which enhances the application security. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. Flash memory up to 2 Mbytes, 5. Kbytes of SRAM including 1. Kbytes of Data TCM RAM for critical real time data, 1. Kbytes of instruction TCM RAM for critical real time routines, 4 Kbytes of backup SRAM available in the lowest power modes, and an extensive range of enhanced IOs and peripherals connected to two APB buses, two AHB buses, a 3. AHB bus matrix and a multi layer AXI interconnect supporting internal and external memories access. All the devices offer three 1. ADCs, two DACs, a low power RTC, twelve general purpose 1. PWM timers for motor control, two general purpose 3. RNG. They also feature standard and advanced communication interfaces. Advanced peripherals include two SDMMC interfaces, a flexible memory control FMC interface, a Quad SPI Flash memory interface, a camera interface for CMOS sensors. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. C temperature range from a 1. V power supply. Dedicated supply inputs for USB OTGFS and OTGHS and SDMMC2 clock, command and 4 bit data are available on all the packages except LQFP1. The supply voltage can drop to 1. V with the use of an external power supply supervisor. A comprehensive set of power saving mode allows the design of low power applications. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. The set of included peripherals changes with the device chosen. These features make the STM3. F7. 65xx, STM3. 2F7. STM3. 2F7. 68. Ax and STM3. F7. 69xx microcontrollers suitable for a wide range of applications. Key Features. Core Arm 3. Cortex M7 CPU with DPFPU, ART Accelerator and L1 cache 1. Kbytes ID cache, allowing 0 wait state execution from embedded Flash and external memories, up to 2. MHz, MPU, 4. 62 DMIPS2. DMIPSMHz Dhrystone 2. DSP instructions. Up to 2 Mbytes of Flash memory organized into two banks allowing read while write. SRAM 5. 12 Kbytes including 1. Kbytes of data TCM RAM for critical real time data 1. Kbytes of instruction TCM RAM for critical real time routines 4 Kbytes of backup SRAMFlexible external memory controller with up to 3. SRAM, PSRAM, SDRAMLPSDR SDRAM, NORNAND memories. Dual mode Quad SPI. Chrom ART Accelerator DMA2. D, graphical hardware accelerator enabling enhanced graphical user interface. Hardware JPEG codec. LCD TFT controller supporting up to XGA resolution. MIPI DSI host controller supporting up to 7. Hz resolution. Clock, reset and supply management. V to 3. 6 V application supply and IOs. Game Shrek Super Slam'>Game Shrek Super Slam. POR, PDR, PVD and BORDedicated USB power. MHz crystal oscillator. Internal 1. 6 MHz factory trimmed RC 1 accuracy3. Hz oscillator for RTC with calibration. Internal 3. 2 k. Hz RC with calibration. Low power. Sleep, Stop and Standby modes. VBAT. supply for RTC, 3. Kbytes backup SRAM31. MSPS ADC up to 2. Digital filters for sigma delta modulator DFSDM, 8 channels 4 filters. DA converters. General purpose DMA 1. DMA controller with FIFOs and burst support. Up to 1. 8 timers up to thirteen 1. Stop mode and two 3. ICOCPWM or pulse counter and quadrature incremental encoder input. All 1. 5 timers running up to 2. MHz. 2x watchdogs, Sys. Tick timer. Debug mode. SWD JTAG interfaces. Cortex M7 Trace MacrocellUp to 1. IO ports with interrupt capability. Up to 1. 64 fast IOs up to 1. MHz. Up to 1. 66 5 V tolerant IOs. Up to 2. 8 communication interfaces. Up to 4 I2. C interfaces SMBusPMBusUp to 4 USARTs4 UARTs 1. Mbits, ISO7. 81. LIN, Ir. DA, modem controlUp to 6 SPIs up to 5. Mbits, 3 with muxed simplex I2. S for audio. 2 x SAIs serial audio interface3 CANs 2. B Active and 2x SDMMCs. SPDIFRX interface. HDMI CECMDIO slave interface. Advanced connectivity. USB 2. 0 full speed devicehostOTG controller with on chip PHYUSB 2. OTG controller with dedicated DMA, on chip full speed PHY and ULPI1. Ethernet MAC with dedicated DMA supports IEEE 1. MIIRMII8 to 1. 4 bit camera interface up to 5. Mbytes. True random number generator. CRC calculation unit. RTC subsecond accuracy, hardware calendar.

C temperature range. A in VBAT mode supply for RTC and 3. A Shutdown mode 5 wakeup pins1. A Standby mode 5 wakeup pins4. A Standby mode with RTC1. A Stop 2 mode, 1. A with RTC1. 00 AMHz run mode LDO Mode3. AMHz run mode 3. V SMPS ModeBatch acquisition mode BAM4 s wakeup from Stop mode. Brown out reset BORInterconnect matrix. Core ARM 3. 2 bit Cortex M4 CPU with FPU, Adaptive real time accelerator ART Accelerator allowing 0 wait state execution from Flash memory, frequency up to 8. MHz, MPU, 1. 00. DMIPS and DSP instructions. Performance benchmark. DMIPSMHz Drystone 2. Core. Mark 3. 4. Core. MarkMHz 8. MHzEnergy benchmark. Clock Sources. 4 to 4. MHz crystal oscillator. Hz crystal oscillator for RTC LSEInternal 1. MHz factory trimmed RC 1Internal low power 3. Hz RC 5Internal multispeed 1. Hz to 4. 8 MHz oscillator, auto trimmed by LSE better than 0. PLLs for system clock, USB, audio, ADCUp to 1. IOs, most 5 V tolerant, up to 1. IOs with independent supply down to 1. V. RTC with HW calendar, alarms and calibration. LCD 8 4. 0 or 4 4. Up to 2. 4 capacitive sensing channels support touchkey, linear and rotary touch sensors. Stop mode, 2x watchdogs, Sys. Tick timer. Up to 1 MB Flash, 2 banks read while write, proprietary code readout protection. Up to 1. 28 KB of SRAM including 3. KB with hardware parity check. External memory interface for static memories supporting SRAM, PSRAM, NOR and NAND memories. Quad SPI memory interface. Rich analog peripherals independent supply. ADC 5 Msps, up to 1. AMsps. 2x 1. 2 bit DAC, low power sample and hold. PGA2x ultra low power comparators. USB OTG 2. 0 full speed, LPM and BCD2x SAIs serial audio interface3x I2. C FM1 Mbits, SMBusPMBus. USARTs ISO 7. 81. LIN, Ir. DA, modem1x LPUART Stop 2 wake up3x SPIs 4x SPIs with the Quad SPICAN 2. B Active and SDMMC interface. SWPMI single wire protocol master IFIRTIM Infrared interface1. DMA controller. True random number generator. CRC calculation unit, 9. ID. Development support serial wire debug SWD, JTAG, Embedded Trace Macrocell. STM3. 2F7. 67. NI High performance and DSP with FPU, ARM Cortex M7 MCU with 2 Mbytes Flash, 2. MHz CPU, Art Accelerator, L1 cache, SDRAM, TFT, JPEG codec, DFSDMThe STM3. F7. 65xx, STM3. 2F7. STM3. 2F7. 68. Ax and STM3. F7. 69xx devices are based on the high performance Arm Cortex M7 3. RISC core operating at up to 2. MHz frequency. The Cortex M7 core features a floating point unit FPU which supports Arm double precision and single precision data processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit MPU which enhances the application security. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. Flash memory up to 2 Mbytes, 5. Kbytes of SRAM including 1. Kbytes of Data TCM RAM for critical real time data, 1. Kbytes of instruction TCM RAM for critical real time routines, 4 Kbytes of backup SRAM available in the lowest power modes, and an extensive range of enhanced IOs and peripherals connected to two APB buses, two AHB buses, a 3. AHB bus matrix and a multi layer AXI interconnect supporting internal and external memories access. All the devices offer three 1. ADCs, two DACs, a low power RTC, twelve general purpose 1. PWM timers for motor control, two general purpose 3. RNG. They also feature standard and advanced communication interfaces. Advanced peripherals include two SDMMC interfaces, a flexible memory control FMC interface, a Quad SPI Flash memory interface, a camera interface for CMOS sensors. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. C temperature range from a 1. V power supply. Dedicated supply inputs for USB OTGFS and OTGHS and SDMMC2 clock, command and 4 bit data are available on all the packages except LQFP1. The supply voltage can drop to 1. V with the use of an external power supply supervisor. A comprehensive set of power saving mode allows the design of low power applications. The STM3. 2F7. 65xx, STM3. F7. 67xx, STM3. 2F7. Ax and STM3. 2F7. The set of included peripherals changes with the device chosen. These features make the STM3. F7. 65xx, STM3. 2F7. STM3. 2F7. 68. Ax and STM3. F7. 69xx microcontrollers suitable for a wide range of applications. Key Features. Core Arm 3. Cortex M7 CPU with DPFPU, ART Accelerator and L1 cache 1. Kbytes ID cache, allowing 0 wait state execution from embedded Flash and external memories, up to 2. MHz, MPU, 4. 62 DMIPS2. DMIPSMHz Dhrystone 2. DSP instructions. Up to 2 Mbytes of Flash memory organized into two banks allowing read while write. SRAM 5. 12 Kbytes including 1. Kbytes of data TCM RAM for critical real time data 1. Kbytes of instruction TCM RAM for critical real time routines 4 Kbytes of backup SRAMFlexible external memory controller with up to 3. SRAM, PSRAM, SDRAMLPSDR SDRAM, NORNAND memories. Dual mode Quad SPI. Chrom ART Accelerator DMA2. D, graphical hardware accelerator enabling enhanced graphical user interface. Hardware JPEG codec. LCD TFT controller supporting up to XGA resolution. MIPI DSI host controller supporting up to 7. Hz resolution. Clock, reset and supply management. V to 3. 6 V application supply and IOs. Game Shrek Super Slam'>Game Shrek Super Slam. POR, PDR, PVD and BORDedicated USB power. MHz crystal oscillator. Internal 1. 6 MHz factory trimmed RC 1 accuracy3. Hz oscillator for RTC with calibration. Internal 3. 2 k. Hz RC with calibration. Low power. Sleep, Stop and Standby modes. VBAT. supply for RTC, 3. Kbytes backup SRAM31. MSPS ADC up to 2. Digital filters for sigma delta modulator DFSDM, 8 channels 4 filters. DA converters. General purpose DMA 1. DMA controller with FIFOs and burst support. Up to 1. 8 timers up to thirteen 1. Stop mode and two 3. ICOCPWM or pulse counter and quadrature incremental encoder input. All 1. 5 timers running up to 2. MHz. 2x watchdogs, Sys. Tick timer. Debug mode. SWD JTAG interfaces. Cortex M7 Trace MacrocellUp to 1. IO ports with interrupt capability. Up to 1. 64 fast IOs up to 1. MHz. Up to 1. 66 5 V tolerant IOs. Up to 2. 8 communication interfaces. Up to 4 I2. C interfaces SMBusPMBusUp to 4 USARTs4 UARTs 1. Mbits, ISO7. 81. LIN, Ir. DA, modem controlUp to 6 SPIs up to 5. Mbits, 3 with muxed simplex I2. S for audio. 2 x SAIs serial audio interface3 CANs 2. B Active and 2x SDMMCs. SPDIFRX interface. HDMI CECMDIO slave interface. Advanced connectivity. USB 2. 0 full speed devicehostOTG controller with on chip PHYUSB 2. OTG controller with dedicated DMA, on chip full speed PHY and ULPI1. Ethernet MAC with dedicated DMA supports IEEE 1. MIIRMII8 to 1. 4 bit camera interface up to 5. Mbytes. True random number generator. CRC calculation unit. RTC subsecond accuracy, hardware calendar.